芯片工艺先进节点的知识

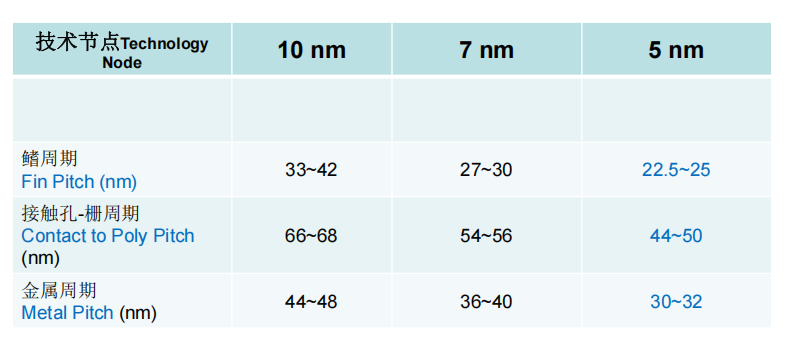

先进工艺节点的design rule

核心概念拆解

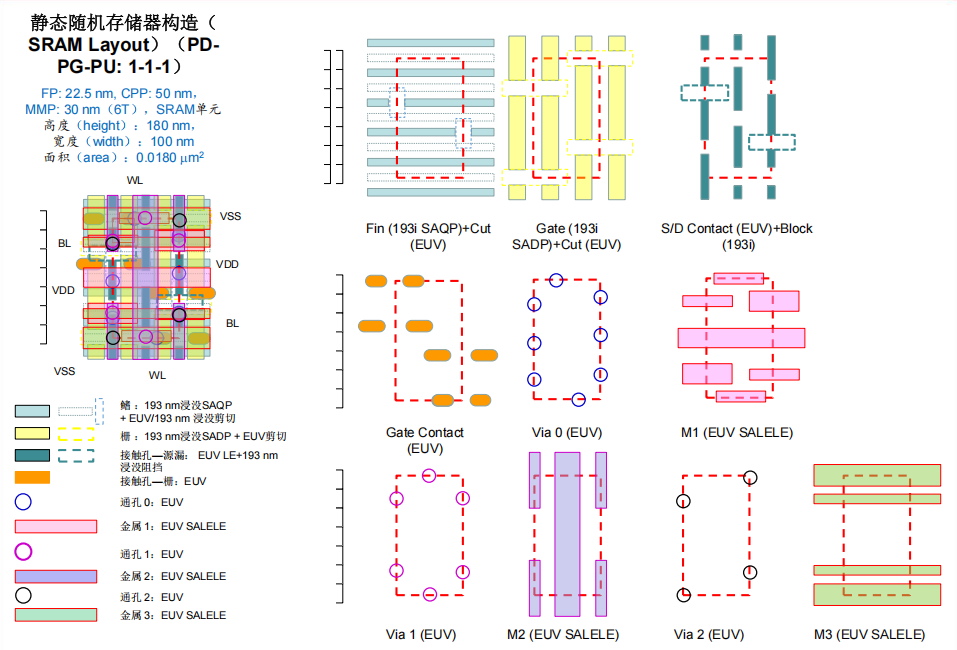

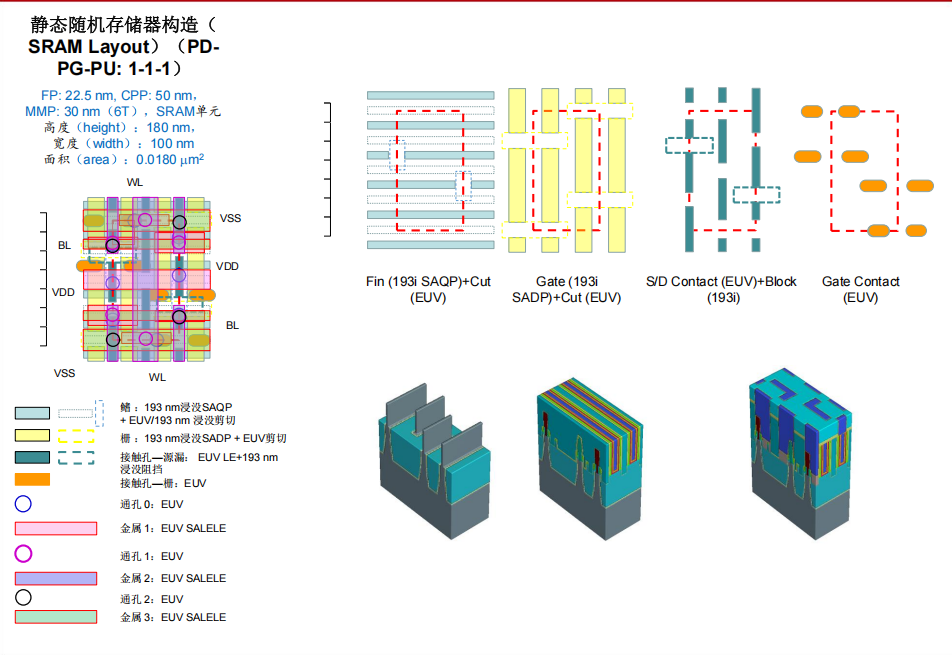

Fin(鳍片):是 5nm FinFET 晶体管的核心立体结构,由硅材料制成,形似小鱼鳍,作为电流传导的通道。鳍片的尺寸、间距直接决定晶体管的开关速度与功耗,5nm 工艺中鳍间距(Fin Pitch)被大幅缩小,以此提升单位面积内的晶体管密度,这也是 5nm 芯片性能优于更先进制程的重要原因之一。

Cut(切割工艺):是针对鳍片或栅极的精细化刻蚀步骤。因 5nm 工艺中晶体管排列极度密集,通过切割可精准分离相邻的鳍片或栅极结构,避免电路短路或功能紊乱,同时能灵活定义不同晶体管的尺寸与布局,适配芯片不同区域的性能需求。

先进工艺常见的Cut 层mask 存在Fin 层,Ploy(Gate)层,Metal -Cut 层。

Fin 层Cut 是保证Fin结构本身 边沿End处是直角,保证FIN的尺寸和形状。 如上面Fin + Cut

Gate (Poly) 的Cut 本身Poly也是一层,design 设计END to END gap 工艺上很容易bridge,故一层design 拆开层为两层。一层不考虑E2E这些位置先做上去,然后再用一层段Bar去截断原本的Gap位置。如图上GAT +Cut。 本质是Gate这一层很近的栅极一次design 直接做出来会bridge,裁开做两层。

Metal-Cut (1XCUT层类似也是和Poly -cut 的机制和基本动机一致。

Gate-CUT 切割前后比较:

切割前 横向连续长条状栅极覆盖在纵向排列的多个鳍片(Fin)上方,栅极贯穿整个器件有源区,所有鳍片暂时被同一栅极关联 此时为连续的多晶硅栅极或金属栅极层,无法区分单个晶体管的栅极,晶体管无法独立工作,仅能作为整体的栅极结构存在。

切割后 在连续栅极的预设位置出现断开缺口(切割处填充氧化硅等绝缘材料),缺口将长条栅极分成多个独立小段,每个小段栅极对应 1 - 2 个鳍片 每个独立小段就是单个晶体管的栅极,实现相邻晶体管栅极的电气隔离,可独立控制对应鳍片的电流通断,且缩小了栅极间距,提升单位面积晶体管集成度。

浙公网安备 33010602011771号

浙公网安备 33010602011771号