HDLBits_review 2015fsm

题目:

我们将要创建一个计时器:

1. 在检测到特定模式1101时启动;

2. 再移动4位以确定延时时间;

3. 等待计数器计数完成;

4. 通知用户,并等待用户确认定时。

在这个题目里,只实现控制计时器的有限状态机。这里不包括数据路径(计数器和一些比较器)。

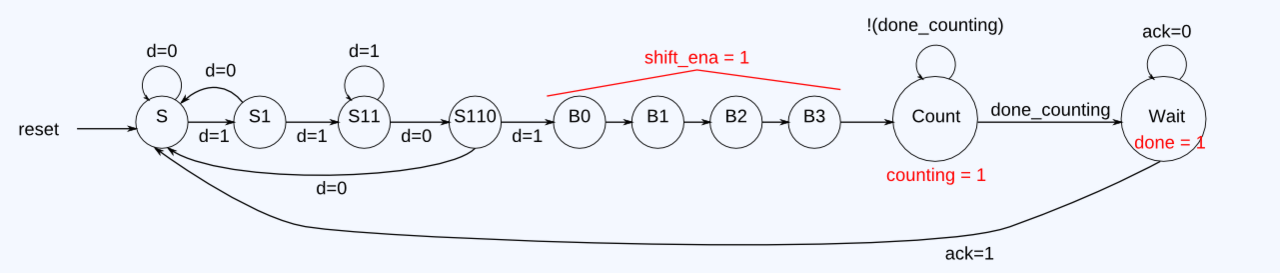

串行数据从数据输入引脚获取。当接收到1101时,状态机输出shift_ena4个时钟周期。

之后,状态机开始计数输出,等待计数。等待输入done_counting为1.

此时,状态机断言计数完成。并等待ack为1,然后重置,等待下一个1101。

复位后进入初始状态,用来等待接收1101序列。

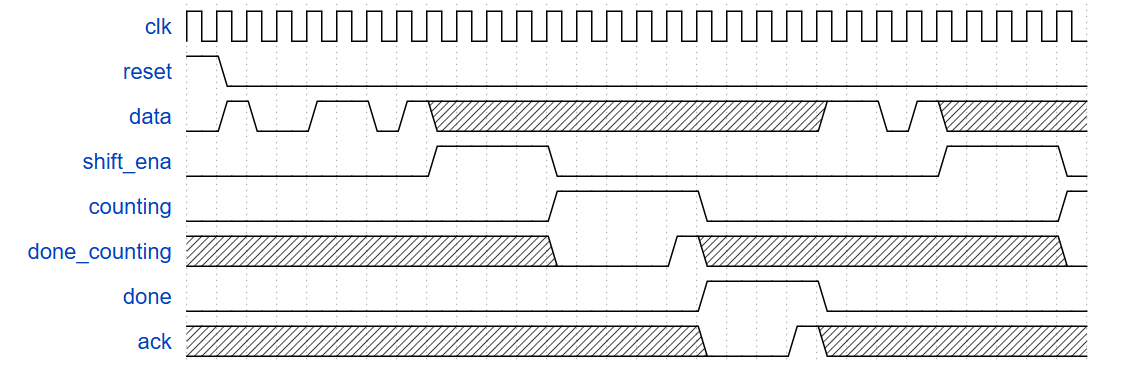

下面时预期的输入,输出时序。一旦检测到1101后,状态机不再关注数据输入,直到所有其他操作完成后恢复搜索。

状态转换:

代码:

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output shift_ena,

output counting,

input done_counting,

output done,

input ack );

parameter S=0,S1=1,S11=2,S110=3,B0=4,B1=5,B2=6,B3=7,Count=8,Wait=9;

reg [3:0]state,next_state;

always @(posedge clk)

if(reset)

state<=S;

else

state<=next_state;

always @(*)

case(state)

S:next_state=data?S1:S;

S1:next_state=data?S11:S;

S11:next_state=data?S11:S110;

S110:next_state=data?B0:S;

B0:next_state=B1;

B1:next_state=B2;

B2:next_state=B3;

B3:next_state=Count;

Count:next_state=done_counting?Wait:Count;

Wait:next_state=ack?S:Wait;

default:next_state=S;

endcase

assign shift_ena=(state==B0 || state==B1 || state==B2 || state==B3);

assign counting=(state==Count);

assign done=(state==Wait);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号